(Artikel überarbeitet und erweitert.) |

BMS (Diskussion | Beiträge) K |

||

| (12 dazwischenliegende Versionen von 2 Benutzern werden nicht angezeigt) | |||

| Zeile 36: | Zeile 36: | ||

|} | |} | ||

| − | Die Eingänge werden mit Set (S) und Reset (R) bezeichnet. Legt man beide Eingänge auf High wird an selbstgebauten (z.B. aus Transistoren oder aus NAND/NOR Gattern) FF ein undefinierter Ausgang erzeugt. Dieser wird deshalb auch als verbotener Zustand bezeichnet. Anders ist das bei fertigen FF aus TTL/CMOS Bausteinen oder beim Programmieren in grafischen Umgebungen (FUP/KOP). Hier werden meist dominante Reset-FF (hier ist der Set Eingang Rezesiv) verwendet, d.h. liegt Set und Reset auf High ist der Ausgang Low. Bei einem FF mit dominanten Set Eingang ist der Ausgang dementsprechend High. In großen Industriesteuerungen wie Simatic S7 sind Flipflops in der Programmierung nicht wegzudenken. | + | Die Eingänge werden mit Set (S) und Reset (R) bezeichnet. Legt man beide Eingänge auf High, wird an selbstgebauten (z.B. aus Transistoren oder aus NAND/NOR Gattern) FF ein undefinierter Ausgang erzeugt. Dieser wird deshalb auch als verbotener Zustand bezeichnet. Anders ist das bei fertigen FF aus [[TTL]]/[[CMOS]] Bausteinen oder beim Programmieren in grafischen Umgebungen (FUP/KOP). Hier werden meist dominante Reset-FF (hier ist der Set Eingang Rezesiv) verwendet, d.h. liegt Set und Reset auf High ist der Ausgang Low. Bei einem FF mit dominanten Set Eingang ist der Ausgang dementsprechend High. In großen Industriesteuerungen wie Simatic S7 sind Flipflops in der Programmierung nicht wegzudenken. |

| − | == Aufbau | + | == Aufbau eines RS-Flipflops == |

==== mit Hilfe von Gattern (Gates) ==== | ==== mit Hilfe von Gattern (Gates) ==== | ||

* 2 NOR-Gates | * 2 NOR-Gates | ||

| Zeile 44: | Zeile 44: | ||

* 2 Nand-Gates | * 2 Nand-Gates | ||

:[[Bild:nand.gif|250px]] | :[[Bild:nand.gif|250px]] | ||

| − | * Aufbau als TTL/CMOS Gatter | + | * Aufbau als [[TTL]]/[[CMOS]] Gatter |

==== mit Hilfe von Transistoren ==== | ==== mit Hilfe von Transistoren ==== | ||

:[[Bild:Bildstabile.png|300px]] | :[[Bild:Bildstabile.png|300px]] | ||

| + | Anmerkung: Vor E1 und E2 sollten Widerstände eingebaut werden, um den Stromfluss durch die Basis zu begrenzen. | ||

| − | == | + | == Latch == |

| − | + | ||

| − | + | ||

| − | + | Eine zum RS-Flipflop ähnliche Funktion ( 1 Bit Speicher) hat das (transparente) Latch. An Stelle von getrennten Eingängen für das Setzen und Löschen haben die beiden Eingänge die Funktion Daten bzw. Speichern (Engl. Enable). | |

| − | + | Solange der Enable Eingang aktiv ist (im allgmeinen H), wird der Wert vom Daten Eingang übernommen und ausgegeben. Wenn der Enable Eingang nicht aktiv ist, behält der Ausgang seinen alten Wert. | |

| − | + | ||

| + | Teilweise haben Latches noch einen zusätzlichen Eingang, um den Ausgang wahlweise auch hochohmig zu schalten (Tristate-Ausgang). | ||

| + | |||

| + | Typische ICs mit dieser Funktion sind 74HC75 und 74HC373. | ||

| + | |||

| + | == Weitere Arten: flankengetriggerte Flipflops == | ||

=== D-Flipflop === | === D-Flipflop === | ||

| − | Ein | + | Ein flankengesteuertes Flipflop mit den Eingängen Data (D) und Clock (C). Das FF kann den Data-Eingang nur zum Ausgang "durchfloppen", wenn der Clock-Eingang eine bestimmte Flanke aufweist. |

| + | Ein typisches IC mit dieser Funktion ist 74HC74. | ||

| + | |||

=== T-Flipflop === | === T-Flipflop === | ||

| − | Toggle-Flipflop. Wie ein D-FF, hat aber nur einen Takt-Eingang (C) und "floppt" bei jedem Takt um. | + | Toggle-Flipflop. Wie ein D-FF, hat aber nur einen Takt-Eingang (C) und "floppt" bei jedem Takt um. Aus einen D-FF wird ein T-FF, wenn man den D Eingang mit dem invertierten Ausgang verbindet. |

| + | |||

| + | === JK-Flipflop === | ||

| + | Das JK Flipflop ist wie das D Flipflop flankengetriggert. Die beiden Eingänge J und K bestimmen was bei einer Flanke (je nach Typ steigend oder fallend) am Takteingang (C) passiert. Sind J und K low, passiert nichts. Sind J und K high, wird der Ausgang invertiert (Toggle-FF). Sind J und K verschieden, wird der Zustand von J an den Ausgang übernommen. Ein Typisches IC mit dieser Funktion ist 74HC107. | ||

| + | |||

| + | == Anwendungen == | ||

| + | * Speichereinheit für ein Signal/Bit | ||

| + | * Register (Mehrere FF's parallel zusammengeschalten) | ||

| + | * Schieberegister (D- FF's seriell zusammengeschaltet) | ||

| + | * Ringregister (Schieberegister, dessen Ausgang wieder mit dem Eingang verbunden ist) | ||

| + | * Teilen einer Frequenz durch 2 (T-Flipflop) | ||

| + | * Synchronisieren von Eingängen (D-Flipflop) | ||

| + | * Binärzähler, Modulo-n-Teiler | ||

== Quellen == | == Quellen == | ||

| Zeile 64: | Zeile 82: | ||

* http://www.iris.uni-stuttgart.de/lehre/eggenberger/ksn/9_Flipflops/NAND-FF.htm | * http://www.iris.uni-stuttgart.de/lehre/eggenberger/ksn/9_Flipflops/NAND-FF.htm | ||

* http://www.mr.inf.tu-dresden.de/lehre_ws/infet1/docs/Kapitel3-Informationsverarbeitung.pdf | * http://www.mr.inf.tu-dresden.de/lehre_ws/infet1/docs/Kapitel3-Informationsverarbeitung.pdf | ||

| + | * [http://www.onsemi.com/pub_link/Collateral/MC74HC73-D.PDF Datenblatt zu JK Flipflop ] | ||

[[Kategorie:Microcontroller]] | [[Kategorie:Microcontroller]] | ||

| + | [[Kategorie:Elektronik]] | ||

Aktuelle Version vom 17. Juli 2011, 19:53 Uhr

Inhaltsverzeichnis

Definition

Das Flipflop (FF) wird auch bistabiler Multivibrator oder bistabile Kippstufe genannt. Dies ist eine elektronische Schaltung, die zwischen zwei möglichen Zuständen umschaltet, wenn ein Impuls am Eingang eintrifft. Ist z.B. der Ausgang eines FF High, kippt ein am Eingang empfangener Impuls den Ausgang auf Low. Ein zweiter Eingangsimpuls »flopt« den Ausgang wieder auf High, usw..

Wahrheitstafel RS-FF

(Q(t)-aktueller Zustand, Q(t+1)-Folgezustand)R S Q(t+1) ¬Q(t+1) Verhalten 0 0 Q(t) ¬Q(t) Speichern 1 0 0 1 Rücksetzen 0 1 1 0 Setzen 1 1 ? ? verbotener Zustand

Die Eingänge werden mit Set (S) und Reset (R) bezeichnet. Legt man beide Eingänge auf High, wird an selbstgebauten (z.B. aus Transistoren oder aus NAND/NOR Gattern) FF ein undefinierter Ausgang erzeugt. Dieser wird deshalb auch als verbotener Zustand bezeichnet. Anders ist das bei fertigen FF aus TTL/CMOS Bausteinen oder beim Programmieren in grafischen Umgebungen (FUP/KOP). Hier werden meist dominante Reset-FF (hier ist der Set Eingang Rezesiv) verwendet, d.h. liegt Set und Reset auf High ist der Ausgang Low. Bei einem FF mit dominanten Set Eingang ist der Ausgang dementsprechend High. In großen Industriesteuerungen wie Simatic S7 sind Flipflops in der Programmierung nicht wegzudenken.

Aufbau eines RS-Flipflops

mit Hilfe von Gattern (Gates)

- 2 NOR-Gates

- 2 Nand-Gates

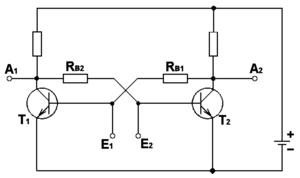

mit Hilfe von Transistoren

Anmerkung: Vor E1 und E2 sollten Widerstände eingebaut werden, um den Stromfluss durch die Basis zu begrenzen.

Latch

Eine zum RS-Flipflop ähnliche Funktion ( 1 Bit Speicher) hat das (transparente) Latch. An Stelle von getrennten Eingängen für das Setzen und Löschen haben die beiden Eingänge die Funktion Daten bzw. Speichern (Engl. Enable). Solange der Enable Eingang aktiv ist (im allgmeinen H), wird der Wert vom Daten Eingang übernommen und ausgegeben. Wenn der Enable Eingang nicht aktiv ist, behält der Ausgang seinen alten Wert.

Teilweise haben Latches noch einen zusätzlichen Eingang, um den Ausgang wahlweise auch hochohmig zu schalten (Tristate-Ausgang).

Typische ICs mit dieser Funktion sind 74HC75 und 74HC373.

Weitere Arten: flankengetriggerte Flipflops

D-Flipflop

Ein flankengesteuertes Flipflop mit den Eingängen Data (D) und Clock (C). Das FF kann den Data-Eingang nur zum Ausgang "durchfloppen", wenn der Clock-Eingang eine bestimmte Flanke aufweist. Ein typisches IC mit dieser Funktion ist 74HC74.

T-Flipflop

Toggle-Flipflop. Wie ein D-FF, hat aber nur einen Takt-Eingang (C) und "floppt" bei jedem Takt um. Aus einen D-FF wird ein T-FF, wenn man den D Eingang mit dem invertierten Ausgang verbindet.

JK-Flipflop

Das JK Flipflop ist wie das D Flipflop flankengetriggert. Die beiden Eingänge J und K bestimmen was bei einer Flanke (je nach Typ steigend oder fallend) am Takteingang (C) passiert. Sind J und K low, passiert nichts. Sind J und K high, wird der Ausgang invertiert (Toggle-FF). Sind J und K verschieden, wird der Zustand von J an den Ausgang übernommen. Ein Typisches IC mit dieser Funktion ist 74HC107.

Anwendungen

- Speichereinheit für ein Signal/Bit

- Register (Mehrere FF's parallel zusammengeschalten)

- Schieberegister (D- FF's seriell zusammengeschaltet)

- Ringregister (Schieberegister, dessen Ausgang wieder mit dem Eingang verbunden ist)

- Teilen einer Frequenz durch 2 (T-Flipflop)

- Synchronisieren von Eingängen (D-Flipflop)

- Binärzähler, Modulo-n-Teiler

Quellen