Inhaltsverzeichnis

Merkmale und Pinbelegung

| Mega 16 | Mega 32 | Mega 644 | |

| Gehäuse | DIL-40 | DIL-40 | DIL-40 |

| MHz | max. 16 | max. 16 | max. 20 |

| Flash | 16 KB | 32 KB | 64 KB |

| EEProm | 512 Byte | 1 KB | 2 KB |

| RAM | 1 KB | 2 KB | 4 KB |

| I/O | 32 | 32 | 32 |

| PWM | 4 | 4 | 6 |

| ext. INT | 3 | 3 | 32 |

Ähnlich dem Mega644 gibt es mit Mega164, Mega324 und Mega1284 auch noch Versionen mit weniger und mehr Speicher.

Einfache Grundschaltung

Weitere Grundschaltungen im Artikel AVR-Einstieg leicht gemacht

Internes zum Atmega32

Wenn man das erste Mal mit solchen komplizierten Geräten wie Micro-Controllern konfrontiert wird, kann es schon sein, daß man vor Ehrfurcht erschaudert. Und auch wenn man von Bits und Bytes durchaus eine Ahnung hat, ist allein schon der Umfang des Datasheets möglicherweise abschreckend. Es soll hier versucht werden darzustellen, daß die ganze Sache nun so schlimm auch wieder nicht ist, wenn man sich den Aufbau eines typischen Vertreters der ATMEL Microcontroller etwas näher betrachtet.

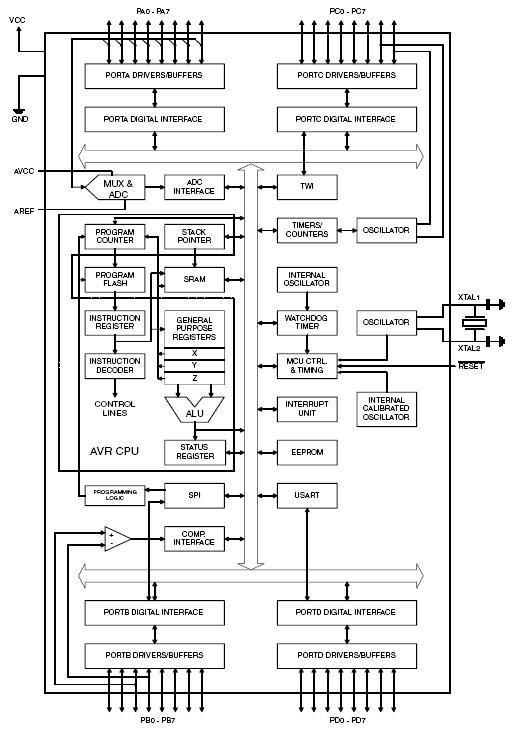

Architektur Überblick

Dieses Bild stammt aus dem Datasheet. Das haben wir wohl schon alle mal gesehen, und vermittelt dem Anfänger eigentlich nur, daß in dem Chip offenbar eine Menge Zeugs drinnen ist. Und da die meisten Pfeile in beide Richtungen zeigen, kann man sich auch nicht recht vorstellen, was da eigentlich in welcher Folge abläuft.

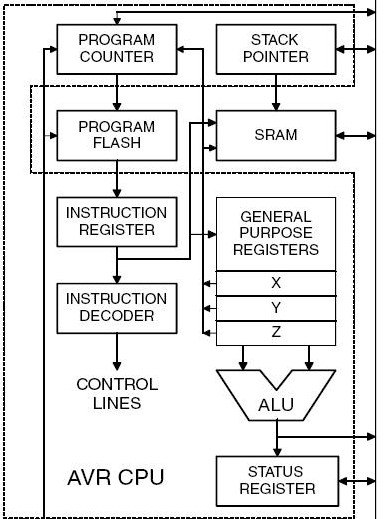

CPU

Das "Herz" des Controllers ist im mittleren Bereich links, das ist die "CPU" (= Zentral-Processor). Von hier aus wird all das Drumherum gesteuert, hier landet das Programm, das wir mit mit irgendeinem Compiler erstellt haben.

Der Rest von dem ganzen Atmega32 ist die "Peripherie", das sind eine Reihe von Einzelgeräten, die alle ihre speziellen Funktionen und Aufgaben haben. Da liegen auch hauptsächlich die Unterschiede zwischen den verschiedenen Micro-Controllern, denn ein kleiner (Tiny) hat weniger solche Geräte und braucht dadurch natürlich auch weniger Pins.

Sehr ähnlich, wenn nicht identisch, ist bei allen AVR-Controllern diese CPU aufgebaut, daher ist es zum Verständnis unerlässlich, sich damit näher zu beschäftigen.

Program Flash

Was da so ein kleines Kästchen ist, das ist der Programmspeicher, der beim Atmega32 immerhin 32k groß ist.

Program Counter

(=Befehlszähler) beinhaltet IMMER die Adresse des nächsten Befehls im Programmspeicher

Instruction Register

hier landet der Inhalt des Programmspeichers von der Adresse "Befehlszähler" immer zuerst, da ja der AVR erstmal selber gucken muß, was für ein Befehl das wohl ist. Jedes Befehlswort beinhaltet (kodiert) drei Dinge: "WAS", "WOHER" und "WOHIN". Einiges kann direkt im SRAM oder in den Register eine Auswahl treffen, einiges muß weiter zum

Instruction Decoder

Je nach Befehl müssen Datenrichtungen eingestellt werden, und etliche Schalter bedient werden. (CONTROL-LINES)

SRAM

Das ist der frei verwendbare Schreib- und Lesespeicher, beim Atmeg32 2k (2048 Byte)

Stack Pointer

Der "Stapel-Zeiger" kann ausschließlich den SRAM adressieren. Aber dazu kommen wir noch

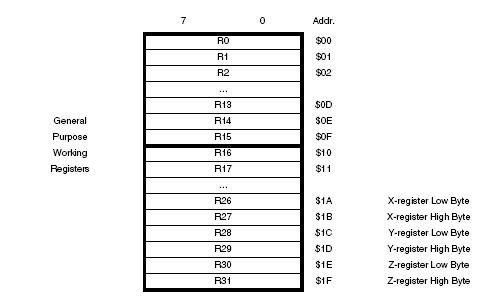

General Purpose Register (GPR)

Wie der Name sagt, das sind 32 Bytes für den allgemeinen Gebrauch. Bezeichnet werden sie als R0 (Addresse $0000) bis R31 (Addresse $001F). Die meisten Maschinenbefehle des AVR beziehen sich darauf, wobei einige Unterschiede zwischen R0 - R15 und R16 - R31 gemacht werden. Für die Register R0-R15 besteht die Einschränkung, das die Befehle mit einer 8 Bit Konstante (z.B. ANDI für die UND-Verknüpfung mit einer Konstante) nicht zur Verfügung stehen. R26 bis R31 können auch als Pointer-Register X, Y u. Z mit ein paar Extras verwendet werden.

ALU

Arithmetische-Logische-Einheit. Die Register R0 - R31 können ihre Werte da anlegen, die ALU macht dann den eigentlichen Befehl damit. Also Addieren, Subtrahieren, usw. Das Ergebnis landet dann wieder in einen der Register R0 - R31. Als Nebenprodukt gibt es zusätzlich ein paar Bits, die im

STATUS REGISTER

landen, wie eben das "ZERO"-Bit, das "CARRY"-Bit usw.

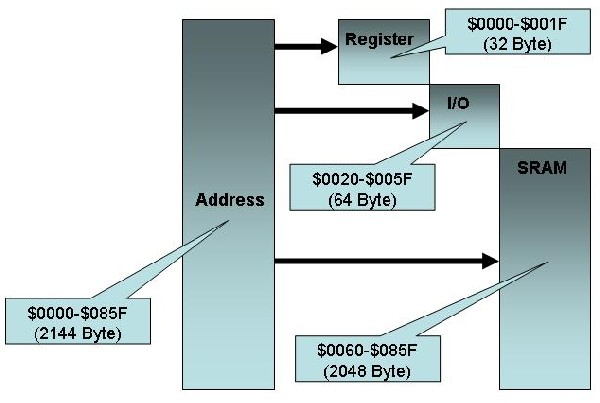

Adressen Mapping

Damit es einfacher ist, Input- und Output-Daten immer ins richtige Kästchen reinzutun oder zu holen, gibt das "Address-Mapping". Es wird einfach eine fortlaufende Adresse angegeben, aber je nach Werte-Bereich landet man ganz woanders.

REGISTER

Das sind die bereits oben erwähnten "Allgemeinen Register" (GPR)

I/O

Wenn man hier schreibt oder liest, landet man in Wirklichkeit bei den Kontroll-Schaltern von einem der "Peripheriegeräte". Da gibt es zum Beispiel Stellen, wenn man da reinschreibt, verändert man irgendeinen PIN aussen am Controller. Auch der Stack-pointer und das Status-Register haben hier einen Platz.

SRAM

ist der auch schon erwähnte frei verfügbare Schreib-und Lesespeicher. Beim einigen neueren µCs beginnt das SRAM erst bei einer etwas höheren Adresse, beim Mega644 z.B. erst bei $0100.

Maschinen-Code

Aufbau

Eine Assembler Source-Zeile, schematisch:

Command Argument1 , Argument2 ; die Argumente sind optionell, je nach Befehl

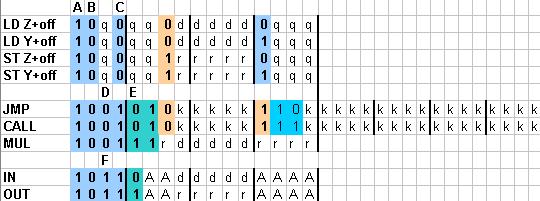

Jede Instruktion ist (mindestens) 16 Bit (zwei Bytes) breit. Hier ein paar Befehle, die Bits in den Spalten von Bit 15 (MSB) bis Bit 0 (LSB), links nach rechts

Der Befehle haben nicht einfach eine Nummer von 0 - 65535, wie man vielleicht erwarten würde, sondern die Befehl-Bits sind mit den Argumenten in recht seltsamer Weise gemischt in diese beiden Bytes hineincodiert. Der Grund ist der, daß die Argumente ja mal mehr, mal weniger Platz beanspruchen, das heißt, für den eigentlichen Befehlscode bleiben u.U. recht wenig Bits übrig.

- Die erste Command-Selektion erfolgt mit den Bits A u. B (s.o.): Im obigen Beispiel steht dort immer "10".

- Dann ist "C" zu prüfen:

Steht dort "0", ist es einer der vier LD/ST Befehle Ist dort aber "1",

- geht es weiter mit den Bits in den Spalten "D" und "E" (und so fort)

Die beiden Befehle "JMP" und "CALL" kommen mit den 16 Bits garnicht aus, da wird auch das nächste Wort gelesen, das den restlichen Teil der Zieladresse beinhaltet. (Dadurch brauchen sie auch einen Clock-Cycle mehr)

Details

Schauen wir uns noch ein paar Bits genauer an.

LD / ST

Die Bits A, B u. C dienen zu Identifizierung. Zur weiteren Unterscheidung bleiben noch die beiden anderen farbig unterlegten Bits

- 27 ==> LD (SRAM --> Register) oder ST (Register --> SRAM)

- 23 ==> Pointer-Register Z oder Y

IN / OUT

Ob IN oder OUT, entscheidet das Bit 211

JMP / CALL

Der einzige Unterschied ist der, ob der aktuelle PC (Program-Count) vor dem Sprung auf den Stack gepusht wird oder nicht (21)

Mehrere Namen für einen Befehl

Bei einer Reihe von Befehlen gibt es mehrere Namen für ein und denselben Maschinenbefehl. Ein Beispiel:

CLR R1 ; (Setze Register 1 auf $00 )

bringt den gleichen Maschinencode wie

EOR R1, R1 ; Register 1 = Register1 "exclusive or" Register1

Besonders im Umfeld des Stausregisters (SREG) kann man fast von einer "Befehlsvermehrung" sprechen. Obwohl es für Setzen, Löschen und Abfragen der Status-Bits entspechenden Maschinencode gibt, tauchen im "Instruction Set" diese Befehle für jedes der Bits einzeln nochmals auf.

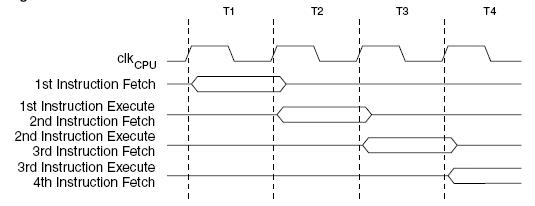

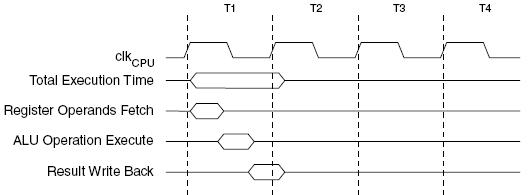

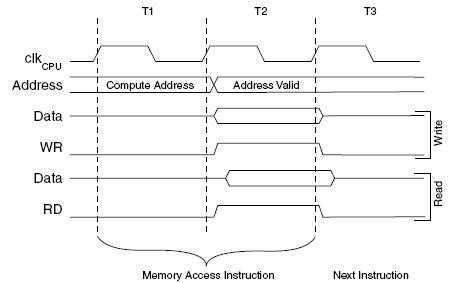

Instruction Cycles

Artikel: PicNick / ergänzt Frank

Siehe auch