(Analog-Digital-Wandler in extra Artikel) |

(Analog Komparator in eingenen Artikel) |

||

| Zeile 50: | Zeile 50: | ||

[[Bild:mega128pin.gif|center]] | [[Bild:mega128pin.gif|center]] | ||

| − | |||

| Zeile 231: | Zeile 230: | ||

== Analog-Komparator == | == Analog-Komparator == | ||

| − | Für | + | Für Infos zu Analog-Komparator siehe Artikel [[Analog Komparator (Avr)]]. |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

== TWI/I2C == | == TWI/I2C == | ||

Version vom 19. November 2006, 17:33 Uhr

AVR ist eine 8-Bit Microcontroller-Familie mit RISC-Architektur. Im Gegensatz zu vielen anderen Microcontroller-Architekturen hat die AVR-Architektur keine Vorgänger. Sie ist ein komplettes Neudesign, das Anfang der 90-Jahre an der Universität von Trondheim/Norwegen entwickelt und vom (bis heute einzigen) Hersteller Atmel aufgekauft wurde. Es gibt eine ganze Serie von AVR-Controllern. Sie alle werden ähnlich programmiert, haben vergleichbaren Befehlssatz und physikalische Eigenschaften, bieten jedoch unterschiedliche Features und Peripherie.

Es gibt zahlreiche und kostenlose Entwicklungssysteme in den Sprachen Basic, C/C++, Pascal und Assembler für diese Controller-Familie.

Inhaltsverzeichnis

Wofür steht AVR?

"AVR" steht angeblich für Advanced Virtual RISC (in einem Paper der Entwickler des AVR-Kerns Alf Egin Bogen und Vegard Wollan). Laut Atmel bedeutet es nichts.

Hardware

AVR-Controller besitzen eine zweistufige Pipeline (fetch and execute), die es ermöglicht, die meisten Befehle innerhalb eines einzigen Prozessortaktes auszuführen. Dadurch ist ein AVR wesentlich schneller als etwa 8051-Controller, bei denen der Prozessortakt intern noch durch 12 geteilt wird.

- AVR-Kern

- Harvard-Architektur (getrennter Befehls- und Datenspeicher)

- 32 Register, kein Akkumulator, 3 Pointerregister

- EEPROM-Datenspeicher

- Watchdog, Bootloader-Support, verschiedene Stromspar-Modi, Brownout-Erkennung, Interner Oszillator

- Lineares Speichermodell (keine Segmentierung)

- 8-Bit Architektur ist für Hochsprachen (C) optimiert

- In-System programmierbar: die Controller können sehr einfach über ein Programmierkabel (oft ISP-Kabel genannt), das mit dem PC verbunden wird, programmiert werden – auch dann, wenn sie sich nicht in einer Schaltung befindet.

- umfangreiche Peripherie

- 8- und 16-Bit-Timer/Counter mit PWM, Capture/Compare, externe Betaktung, asynchrone Operation

- Kommunikation: USART, SPI, I2C (TWI)

- Analog-Comparator, Analog-Digital-Wandler

- unterschiedlichste externe und interne Interrupt-Quellen (UART, SPI, Timer, A/D-Wandler, Analog-Comparator, ...)

- JTAG (Debugerinterface)

- AVR Typen (AT90 "Classic AVR", ATtiny, ATmega)

- erhältlich in unterschiedlichen Gehäusen, idR Durchsteck und als SMD

- Viele Entwicklungsboards erhältlich, z.B. das Roboternetzboard RN-Control

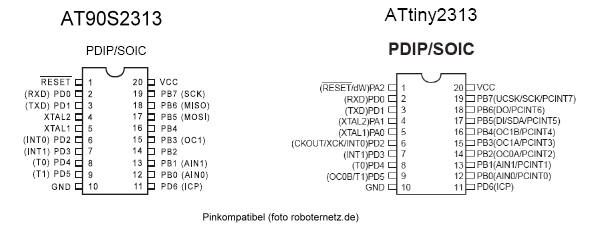

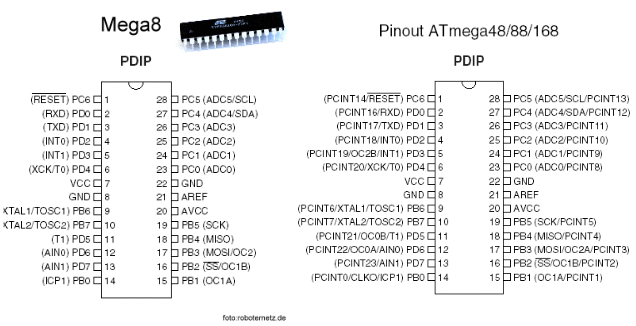

Einige Pinbelegungen der populärsten AVR-Controller

(in etwa nach Leistungsfähigkeit sortiert)

- Atmel Controller Mega128 (SMD-Chip)

Die AVR-Pin-Bezeichnungen und deren Funktion

Die meisten Ports sind doppelt belegt und besitzen neben der normalen Port-Funktion noch eine Sonderfunktion. Die verschiedenen Pinbezeichnungen und Sonderfunktionen werden hier beschrieben:

| Versorgungs- und Referenzpins, Reset | |

|---|---|

| VCC | Versorgungsspannung von 2,7 Volt bis 6 V bei den L-Varianten (low power), ansonsten 4,5V bis 6V. Die nächste AVR-Generation soll ab 1,8 Volt funktionieren. |

| GND | Masse |

| AREF | Referenzspannung für den Analog-Digital-Wandler (kann auf 5V gesetzt werden). Auch die interne Bandgap-Referenzspannung kann über diesen Pin entstört werden (dann KEINE externe Spannung an diesen Pin geben (Kurzschluss)!). |

| AGND | Alternative Masse, etwa um ein Verbindungspunkt mit GND zu haben und bei empfindlichen Messungen Masseschleifen zu vermeiden. |

| AVCC |

Die Betriebsspannung für den Analog-Digital-Wandler (siehe Beschaltungsskizze). Die Pins AVCC, AGND und AREF sollten immer beschaltet werden, da es sonst passieren kann, dass Port A nicht richtig funktioniert, selbst wenn man den AD-Wandler nicht benutzt. |

| RESET | Rücksetz-Eingang, intern über einen Pullup mit VCC verbunden. Ein LOW–Pegel an diesem Pin für die Dauer von mindestens zwei Zyklen des Systemtaktes bei aktivem Oszillator setzt den Controller zurück. Rücksetzen der Ports erfolgt unabhängig von einem evtl. anliegenden Systemtakt. |

| PEN | Programming Enable - Diesen Pin gibt es nur beim Mega128/64 u.ä. Wird dieser Pin beim Power-On Reset nach Masse gezogen, geht der Controller in den ISP Programmiermodus. Man kann ihn also alternativ zu Reset verwenden. In der Regel verwendet man aber die Reset-Leitung und PEN sollte man direkt mit VCC verbinden. |

| System-Takt | |

| XTAL1 | Eingang des internen Oszillators zur Erzeugung des Systemtaktes bzw. Eingang für ein externes Taktsignal, wenn der interne Oszillator nicht verwendet werden soll bzw. Anschluss von Quarz/Keramik-Resonator/RC-Glied. |

| XTAL2 | Anschluss von Quarz oder Keramik-Resonator oder Ausgang des integrierten Oszillators zur Nutzung als Systemtakt (Je nach Fuse-Einstellungen). |

| Digitale bidirektionale I/O-Ports | |

| Jeder Pin der Ports kann individuell als Eingang oder Ausgang konfiguriert werden. Die I/O-Ports sind maximal 8 Bit breit und verfügen ja nach AVR-Typ über eine unterschiedliche Anzahl von Pins. An jedem als Eingang (Input) geschalteten Pin gibt es zuschaltbare Pullup-Widerstände, die teilweise auch bei aktivierter Sonderfunkton verfügbar sind.

Bei eingeschalteten Sonderfunktionen wie UART, SPI, ADC, etc. sind die entsprechenden Pins nicht als "normale" digitale I/O verwendbar, sondern dienen der Sonderfunktion. Die Anzahl der als I/O verwendbaren Pins ist auch abhängig von den Fuse-Einstellungen (Vorsicht beim Umstellen, Handbuch GENAU lesen!). | |

| PA 0 – 7 | Port A |

| PB 0 – 7 | Port B |

| PC 0 – 7 | Port C |

| PD 0 – 7 | Port D |

| PE 0 – 7 | Port E |

| PF 0 – 7 | Port F |

| PG 0 – 7 | Port G |

| Externe Interrupts | |

| Die PCINT-Interrupts gibt es nur für neuere AVRs wie den ATmega88. Falls die Anzahl an externen Interrupts nicht ausreicht, kann evtl. auch andere Hardware dafür eingesetzt werden, etwa der Analog-Comparator mit interner Bandgap-Referenz, falls er anderwärtig nicht gebraucht wird. | |

| INT0 | Externer Interrupt 0 |

| INT1 | Externer Interrupt 1 |

| INT2 | Externer Interrupt 2 |

| PCINTx | Pin-Change Interrupt |

| Timer und PWM | |

| T0 | Timer-Eingang. Timer kann gestartet, gestoppt oder getaktet werden |

| T1 | Timer-Eingang. Timer kann gestartet, gestoppt oder getaktet werden |

| OC0 | PWM bzw. Output Compare Ausgang des Timers 0 |

| OC1A | Ausgang für die Compare-Funktion des integrierten Zeitgeber- / Zählerbausteines

Der erste PWM-Ausgang des Timers1. Er kann zum Regeln der Bot-Motogeschwindigkeit benutzt werden. |

| OC1B | Ausgang für die Compare-Funktion des integrierten Zeitgeber- / Zählerbausteines

Der zweite PWM-Ausgang des Timers1. Er kann zum Regeln der Bot-Motogeschwindigkeit benutzt werden. |

| ICP1 | Eingang für die Capture-Funktion des integrierten Zeitgebers / Zählerbausteines |

| OC2 | Pwm bzw. Output Compare Ausgang des Timers2. Er kann zum Regeln der Bot-Motogeschwindigkeit benutzt werden. |

| TOSC1, TOSC2 | TOSC1 und TOSC2 sind Eingänge für den asynchronen Modus von Timer2. Sie sind vorgesehen für den Anschluss eines externen Uhrenquarzes ( 32.768 kHz ). Damit lassen sich zum Beispiel sehr genaue Ein-Sekunden-Impulse für eine Uhr generien. |

| Analog-Digital-Wandler | |

| ADC0 bis ADC7 | Eingänge des AD-Wandlers. Spannungen können hier gemessen werden oder an den Analog-Komparator weiter geleitet werden. |

| Analog-Komparator | |

| AIN0, AIN1 | Die beiden externen Eingänge des Analog-Komparators.

Mit AIN0(+) und AIN1(-) kann man zwei Spannungen miteinander vergleichen. Wenn die Spannung an AIN0 höher als bei AIN1 ist, liefert der Komparator "High", ansonsten ein "Low". Als interne Eingänge des Komparators können die Interne Bandgap-Referenzspannung oder Ausgänge des ADC-Multiplexers dienen. |

| Serielle Schnittstelle (USART) | |

| RXD | Eingang der Seriellen Schnittstelle (Receive Data), TTL-Pegel |

| TXD | Ausgang Serielle Schnittstelle (Transmit Data), TTL-Pegel |

| XCK | Externe Takt für den USART. Wird nur in Sonderfällen für den Takt benötigt.

USART ("Universal Synchronous/Asynchronous Receiver and Transmitter"). Das ist die serielle Schnittstelle, die zur Datenübertragung zwischen Mikrocontroller und PC genutzt wird. Zur bidirektionalen Übertragung werden zwei Pins am Controller benötigt: TXD und RXD. Über TXD ("Transmit Data") werden Daten gesendet, RXD ("Receive Data") dient zum Empfang. |

| SPI-Schnittstelle | |

| SS | SPI-Interface – wird beneötigt um den richtigen Slave am Bus zu wählen |

| MOSI | SPI-Interface – Datenausgang (als Master) oder Dateneingang (als Slave), verwendet bei ISP (In-System-Programmierung) |

| MISO | SPI-Interface – Dateneingang (als Master) oder Datenausgang (als Slave), verwendet bei ISP (In-System-Programmierung) |

| SCK | SPI-Interface – Bustakt vom Master, verwendet bei ISP (In-System-Programmierung) |

| I2C-Schnittstelle (TWI) | |

| SDA | I2C-Schnittstelle (Bus aus 2 Leitungen) Datenleitung |

| SCL | I2C-Schnittstelle (Bus aus 2 Leitungen) Clockleitung |

| JTAG-Interface | |

| TDI | JTAG-Debug Interface - Über dieses Interface kann man den AVR programmieren und debuggen. Die Schnittstelle ist ähnlich wie die SPI Schnittstelle und hat getrennte Dateneingangs- und Datenausgangsleitungen sowie eine Taktleitung. TDI ist die Dateneingangsleitung |

| TDO | JTAG-Debug Interface - TDO ist die Datenausgangsleitung des JTAG Interface |

| TMS | JTAG-Debug Interface |

| TCK | JTAG-Debug Interface |

Timer/Counter

Für Infos zu Timer und Counter siehe Artikel Timer/Counter (Avr).

Analog-Digital-Wandler

Für Infos zu Analog-Digital-Wandler siehe Artikel ADC (Avr).

Analog-Komparator

Für Infos zu Analog-Komparator siehe Artikel Analog Komparator (Avr).

TWI/I2C

Für Details über das Two-wire Serial Interface (kurz TWI) siehe Artikel TWI.

UART/USART

Für Details über den UART/USART siehe Artikel UART.

SPI - Serial Peripheral Interface

Für Details über SPI siehe Artikel SPI.

Näheres zu SPI beim AVR siehe SPI (AVR).

USI - Universal Serial Interface

Für Infos zu USI (Universal Serial Interface) siehe Artikel USI (Avr).

Die Fusebits

Fusebits nennt man bestimmte Bits zur Konfigurierung eines AVR-Controllers. Bei der Auslieferung neuer AVR Controller sind die Fusebits bereits vorkonfiguriert. In vielen Fällen kann man die Konfiguration unverändert belassen, je nach Controllertyp. Bei den Typen Mega xxx bestimmen einige Fusebits beispielsweise, dass der interne Taktgeber aktiviert ist. Möchte man dagegen einen externen Quarz anschließen oder die Taktfrequenz ändern, so müssen auch die Fusebits geändert werden. Auch das Deaktivieren des "On Chip Debugging" Modus ist oft notwendig, wenn man alle Ports ausnutzen möchte.

Die Fusebits werden in der Regel über die Software eingestellt, welche auch für das Übertragen des Programmcodes zuständig ist. Besonders einfach geht dies beispielsweise mit der Entwicklungsumgebung Bascom. Aber auch andere Programme wie PonyProg können für die Umstellung der Fusebits genutzt werden. Einmal eingestellte Fusebits bleiben bis zur erneuten Fusebit-Änderung erhalten. Der normale Programmiermodus verändert die Fusebits nicht.

Je nach AVR Controllertyp sind unterschiedliche Fusebits (Einstellungen) vorhanden. Die genaue Beschreibung findet man im jeweiligen Datenblatt. Da aber falsch gesetzte Fusebit-Einstellungen zu den häufigsten Problemen gehören, liste ich hier die Funktion der üblichen Fusebits nochmals genauer auf:

| CKSEL0, CKSEL1, CKSEL2, CKSEL3 | Die Kombination dieser 4 Fusebits bestimmt die Taktquelle des Controllers. Das kann eine interner Taktgenerator, ein Quarz, Quarzoszillator, RC-Glied und ähnliches sein. |

| JTAGEN | Hiermit wird die "On Chip Debugging" Schnittstelle aktiviert bzw. deaktiviert. Das sind die Bits mit den Bezeichnungen TDI, TDO, TMS und TCK. Möchte man diese Pins als normalen Port nutzen, so muss diese Schnittstelle immer deaktiviert werden. |

| SUT0, SUT1 | Die sogenannte StartUp-Zeit (PowerOn delay). Diese Einstellung muss abhängig von der Art des Taktgenerators eingestellt werden, genaueres im jeweiligen Datenblatt. |

| SPIEN | Hiermit kann die serielle ISP-Programmierung, welche die meisten Programmierkabel nutzen, deaktiviert werden. Dies sollte man lieber vermeiden, denn wenn dieser Programmiermodus deaktiviert wurde, kann nur noch der Parallel-Programmiermodus genutzt werden. Der Parallel-Programmiermodus benötigt jedoch ein spezielles Programmiergerät, das die wenigsten Bastler besitzen. Also Vorsicht! |

| BODEN | Über dieses Bit wird der Brown-out Detector aktiviert bzw. deaktiviert. Dies ist eine Überwachung der Betriebsspannung. Diese Überwachung soll dafür sorgen, dass bei Spannungseinbrüchen ein ordentlicher RESET durchgeführt wird. Dadurch wird verhindert, dass ein Controller in einen undefinierten Zustand gerät (hängen bleibt). |

| BOOTLEVEL | Über dieses Bit kann die Spannung festgelegt werden, ab welcher der Brown-out Detector den Controller neu startet (also RESET ausführt). |

| BOOTRST | Gewöhnlich startet ein Programm im Controller nach einem RESET ab Adresse 0. Durch dieses Fusebit kann der Controller jedoch veranlasst werden, nach einem Reset einen sogenannten Bootloader-Bereich auszuführen. Ein Bootloader kann genutzt werden, um Controller über andere Schnittstellen (z.B. RS232) zu programmieren. |

| BOOTSZ0, BOOTSZ1 | Der zuvor genannte Bootloaderbereich kann bei AVR-Controllern verschieden groß sein. Über diese beiden Bits können vier verschiedene Größen eingestellt werden. Siehe unter Bootloader. |

| EESAVE | Dieses Bit legt fest, ob beim Programmieren des Controllers (man nennt es auch brennen) immer das EEPROM gelöscht werden soll. |

| CKOPT | Abhängig von den Einstellungen von CKSEL kann hier dir Oszillator-Verstärkung eingestellt werden. Genaueres im Datenblatt des jeweiligen Controllers. |

| WDTON | Schaltet den WatchDog-Timer beim Booten ein/aus. Dies ist auch per Software möglich |

| RSTDISBL | Durch dieses Bit kann man den RESET-Pin deaktivieren und dann als normalen I/O-Port nutzen. Aber Vorsicht! Da die RESET-Leitung beim Programmieren (Brennen) des Chips genutzt wird, kann man nach dessen Deaktivierung den Controller mit den üblichen ISP-Adaptern nicht mehr programmieren. In diesem Fall könnte man zwar den Controlle noch mit speziellen Programmiergeräten im Parallelmodus programmieren, aber in der Praxis verfügen nur wenige Bastler über ein Programmiergerät, das dies leistet. |

| LB1, LB2 | Das sind die sogenannten Lockbits, mit denen sich das Auslesen des Flash- als auch EEPROM-Speichers verhindern läßt. Zwar können andere Anwender immer noch Daten lesen, allerdings handelt es sich dabei nicht mehr um den wirklichen Inhalt sondern lediglich um wirre Datenbytefolgen. Programmierer, die den erarbeiteten Code vor Raubkopierern schützen wollen, nutzen diese Lockbits. Das Programmieren ist auch bei gesetzen Lockbits noch möglich. Der Bootloader-Bereich wird nicht durch die Lockbits geschützt. |

| BLB01, BLB02 | Durch diese Bits kann der Code sogar vor dem Zugriff durch den Bootloader geschützt werden |

| BLB11, BLB12 | Diese Bits schützen den Bootloaderbereich selbst |

Wie man die Fusebits mit Bascom einstellt, wird im Beitrag Bascom - Erstes Programm in den AVR Controller übertragen erläutert.

Autoren des Artikels: Frank, Luma

Siehe auch

Entwicklungsumgebungen

- Bascom - Basic-Entwicklungssystem

- Bascom - Erstes Programm in den AVR Controller übertragen

- avr-gcc - Leistungsfähiger AVR-Port des freien Compilers GCC

- WinAVR - Freies, kostenloses Werkzeugpaket mit avr-gcc, binutils, tools (make, Programmer's Notepad, avrdude, etc.) für MS-Windows.

- AVR Assembler Einführung (AvrStudio)

Hardware

- AVR-ISP Programmierkabel - Bauanleitung für die AVR Controller Programmierkabel

- RN-Control - Eines der beliebtestet AVR-Boards im Roboternetz

- RNBFRA-Board - Größeres Board mit zwei Atmel Controllern

Sonstiges

Weblinks